# ON-CHIP ADVANCED CONTROL ALGORITHM FOR MEMRISTOR OPERATIONS WITH INTEGRATED RISC-V CORE

Wei Zhao<sup>1</sup>, Neethu Kuriakose<sup>1</sup>, Sabitha Kusuma<sup>1</sup>, Abdelaziz Ammari<sup>1</sup>, , Arun Ashok<sup>1</sup>, Christian Grewing<sup>1</sup>, Andre Zambanini<sup>1</sup>, Stefan van Waasen<sup>1,2</sup>

<sup>1</sup> Central Institute of Engineering, Electronics and Analytics ZEA-2 – Electronic Systems, Forschungszentrum Jülich GmbH, Germany

<sup>2</sup> Communication Systems Department (NTS), University of Duisburg-Essen

### **KEY RESULTS**

array with precision.

Enabled both voltage and current control modes for the analog conductance control.

RISC-V core to manage a 2×2 memristor

- Improved memory performance through dynamic configuration of pulse parameters.

- Validated the accuracy and reliability of control signals using a Universal Verification Methodology Framework (UVMF) testbench.

- Demonstrated the potential of RISC-V and memristor integration for scalable memory systems and neuromorphic computing applications.

#### INTRODUCTION

As Moore's law encounters fundamental physical limitations, alternative computational approaches, such as neuromorphic computing using elementary memristors, are gaining traction in the scientific community due to several distinct advantages:

- Scalability

- Compatibility with CMOS Technology

#### **Key Challenges:**

**CMOS-Based Control Circuitry:** Managing analog conductance in memristors requires further research in control systems

#### **Project Focus:**

- Flexible Control Architecture:

- Utilizing a RISC-V core for adaptable control

- Designed for both voltage and current control modes in a 2×2 memristor array

#### **Objectives:**

Develop a flexible control based on Soc

### **DISCUSSION AND FUTURE RESEARCH**

- So far, successful control of Low Resistance State (LRS) and High Resistance State (HRS) has been achieved, validating the control system's basic functionality.

- However, precise control of intermediate resistance states remains a challenge and requires further investigation to enable multilevel memory storage.

- Implementing an error correction algorithm may become essential to improve accuracy and reliability in managing these intermediate states, ensuring consistent performance across various applications.

#### **METHODOLOGY**

2 CHANNEL **DIG\_TOP** ADC CTRL MEMRISTOR\_CTRL AE1 Memristor SRAM: **RISC-V Data Memory** AE2 **Memristor** MEMCTRL\_CTRL **Instruction Memory** Analog Memristor **CONFIG MCTRL** APB Control Memristor Block **PWM JTAG**

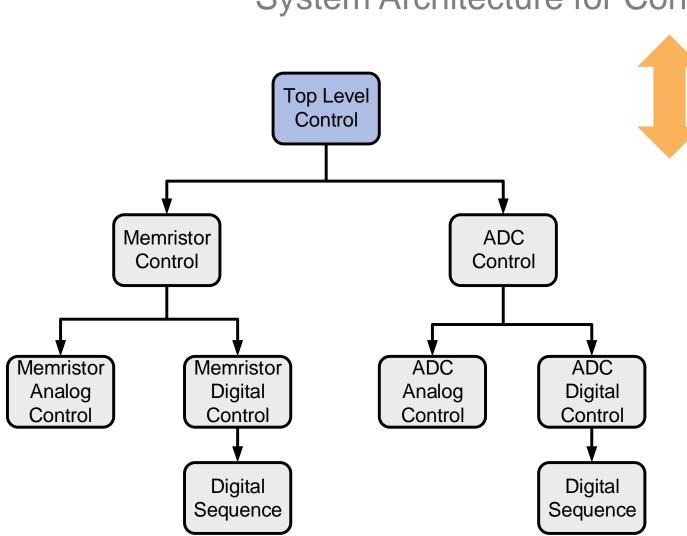

System Architecture for Controlling a 2×2 Memristor Array

- Top Level Control: Directs both memristor and ADC controls.

- Memristor Control: Includes analog and digital control functions for setting memristor states, along with a digital sequence for operation flow.

- ADC Control: Manages analog and digital readout of memristor states, with a digital sequence for readout processes.

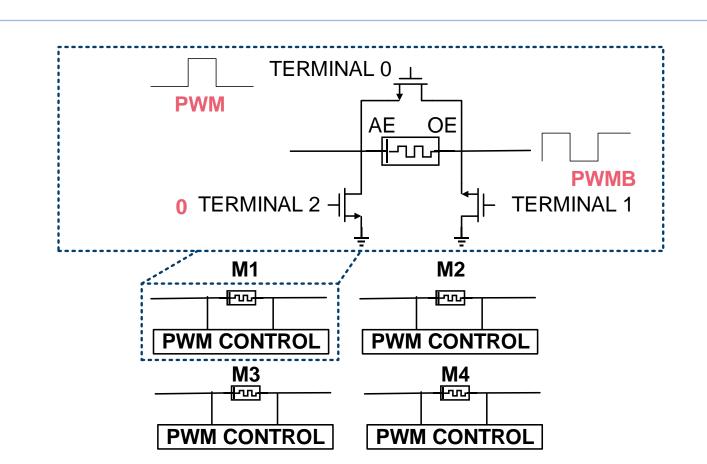

- Memristors M1, M2, M3, and M4 are arranged in a 2x2 grid and are controlled by the PWM signals generated by PWM generator.

- The PWM signals are sent to the transmission gates of the corresponding memristors to set, reset, or read each memristor.

## INITIALIZATION **ELECTROFORMING MEMRISTOR SELECTION** RD/WR MODE RESISTANCE **READ** WR REQUIRED? NO **END**

- Initialization: Configure system settings and pulse parameters.

- **Electroforming:** Active the memristors.

- Memristor Selection: Choose the specific memristor(s) to operate on.

- Write (WR): Select the operation mode (Voltage, or Current) and execute the write operation.

- Read (RD): Measure the resistance state of the selected memristor.

- Verification: End the process if the memristor has reached the target state (YES). If the target state is not reached (NO), repeat the write-read sequence until successful.

Wei Zhao Master Student at TUM

w.zhao@fz-juelich.de

**Electronic Systems (ZEA-2)** www.fz-juelich.de/en/zea/zea-2

V MODE/I MODE

**VAR MODE**

RESET/SET

YES

This research work within the NEUROTEC II project is funded by the German Federal Ministry of Education and Research (BMBF) with grant number

[1] P. Mazumder, S.-M. Kang, R. Waser, "Memristors: Devices, Models, and Applications [Scanning the Issue]" Proc. IEEE, vol. 100, pp. 1911-1919, 2012, doi: 10.1109/JPROC.2012.2190812 [2] K. Higuchi, T. Iwasaki, K. Takeuchi, "Verify-Programming Methods for 50nm HfO2 ReRAM" IEEE Int. Mem. Workshop, Milan, 2012, pp. 1-4, doi: 10.1109/IMW.2012.6213665

[3] H. García, S. Dueñas, Ó. G. Ossorio, H. Castañ, "Current Pulses to Control Conductance in RRAM Devices" IEEE J. Electron Devices Soc., vol. 8, pp. 291-296, 2020, doi: 10.1109/JEDS.2020.2979293 [4] C. Bengel, A. Siemon, F. Cüppers, et al., "Variability-Aware Modeling of Filamentary Oxide-Based Bipolar Resistive Switching Cells" IEEE Trans. Circuits Syst. I, 2020, doi: 10.1109/TCSI.2020.3018502

[5] J. Mair, S. Kusuma, D. Liebau, et al., "Rapid Prototyping Platform for ICs in Quantum Computing" SMACD 2024 [6] L. Vandelli, A. Padovani, L. Larcher, et al., "Modeling of Forming Operation in HfO2 Resistive Memories" IEEE Int. Mem. Workshop, 2011, doi: 10.1109/IMW.2011.5873224 [7] B. Q. Le, et al., "RADAR: Energy-Efficient Programming for RRAM Arrays" IEEE Trans. Electron Devices, vol. 68, no. 9, pp. 4397-4403, 2021, doi: 10.1109/TED.2021.3097975

[8] J. Büchel, et al., "Gradient Descent-Based Programming for Analog In-Memory Computing" IEEE Int. Electron Devices Meeting, 2022, doi: 10.1109/IEDM45625.2022.10019486